**Instruction Manual**

### Tektronix

# TMS 810 Rambus Direct RIMM Memory Bus Support 071-0471-02

Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

www.tektronix.com

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### SOFTWARE WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) months from the date of shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### HARDWARE WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

### **Table of Contents**

|                         | General Safety Summary                                                                                                                                          | V                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|                         | Service Safety Summary                                                                                                                                          | vii                                                                           |

|                         | Preface                                                                                                                                                         | <b>ix</b><br>ix<br>x                                                          |

| Getting Started         |                                                                                                                                                                 |                                                                               |

|                         | Support Package Description                                                                                                                                     | $1-1 \\ 1-1 \\ 1-1 \\ 1-2 \\ 1-2 \\ 1-2 \\ 1-8 \\ \dots 1-10 \\ 1-12 \\ 1-33$ |

| <b>Operating Basics</b> |                                                                                                                                                                 |                                                                               |

|                         | Setting Up the Support<br>Installing the Support Software<br>Channel Group Definitions<br>Clocking<br>Triggering<br>Symbols<br>Timing Alignment Between Packets | <b>2–1</b><br>2–1<br>2–2<br>2–3<br>2–8<br>2–15                                |

|                         | Acquiring and Viewing Disassembled DataAcquiring DataViewing Disassembled DataViewing an Example of Disassembled DataSetup and Display for Cross-Trigger        | <b>2–17</b><br>2–17<br>2–17<br>2–19<br>2–19                                   |

| Specifications          |                                                                                                                                                                 |                                                                               |

| Maintenance             | Specification Tables Dimensions                                                                                                                                 | 3–1<br>3–4                                                                    |

| Schematics              | Replacing the Fuse                                                                                                                                              | 4–1                                                                           |

| Replaceable Parts List  |                                                                                                                                                                 |                                                                               |

| Index                   |                                                                                                                                                                 |                                                                               |

### List of Figures

| Figure 1–1: Identify slot(s) for probe adapter insertion<br>(front of board) | 1–4  |

|------------------------------------------------------------------------------|------|

| Figure 1–2: Identify slot(s) for probe adapter insertion                     |      |

| (back of board)                                                              | 1–5  |

| Figure 1–3: Connecting the probe adapter to the                              |      |

| system under test                                                            | 1-6  |

| Figure 1–4: Connecting a probe to the connector on the                       |      |

| probe adapter                                                                | 1–7  |

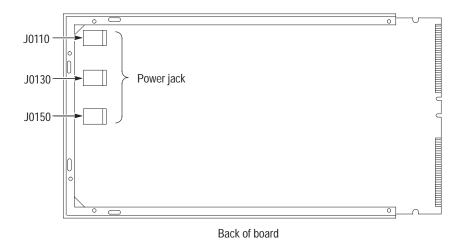

| Figure 1–5: Location of the power jacks                                      | 1–9  |

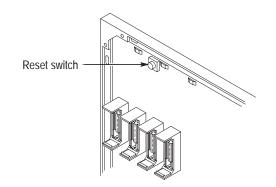

| Figure 1–6: Location of the Reset switch                                     | 1–10 |

|                                                                              |      |

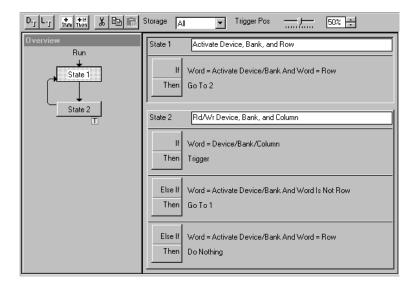

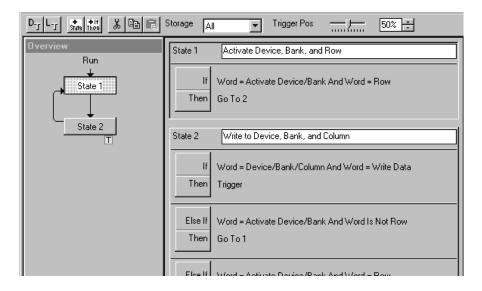

| Figure 2–1: Load logic analyzer trigger                                      | 2–4  |

| Figure 2–2: Trig_ROW_COL                                                     | 2–5  |

| Figure 2–3: Trig_ROW_COL_WD                                                  | 2–6  |

| Figure 2–4: Disassembled display format                                      | 2–18 |

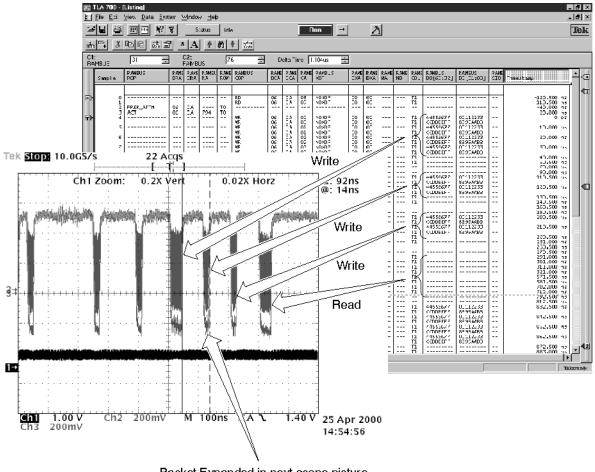

| Figure 2–5: Data bits displayed on the oscilloscope                          | 2–23 |

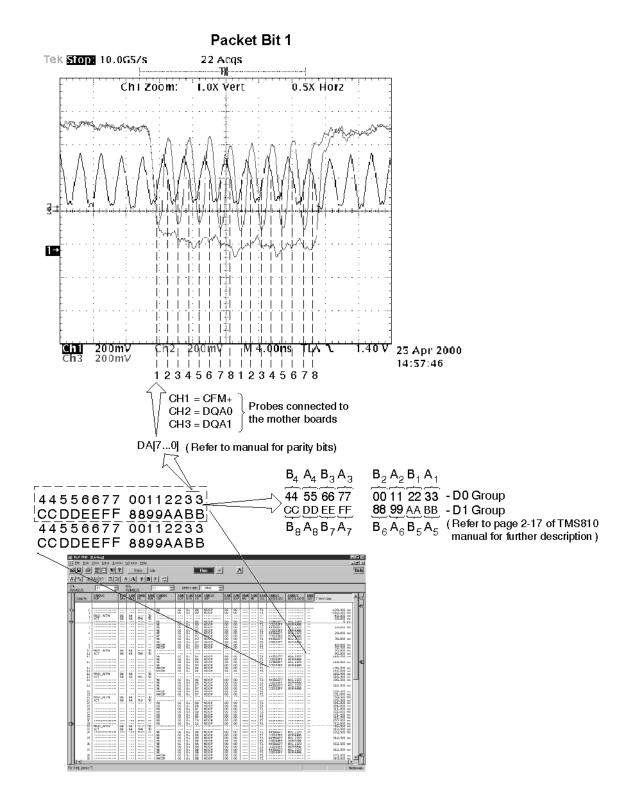

| Figure 2–6: Expanded View of Packet Bit 1                                    | 2–24 |

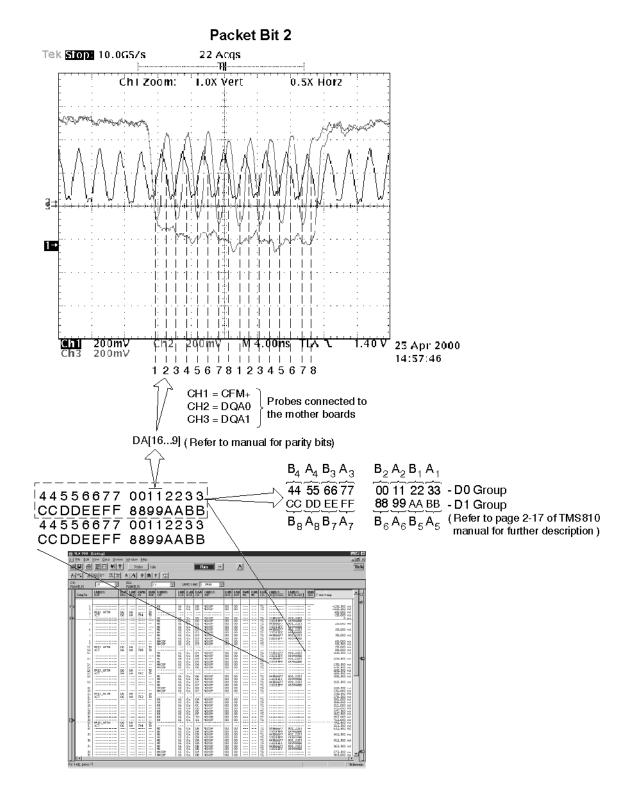

| Figure 2–7: Expanded View of Packet Bit 2                                    | 2–25 |

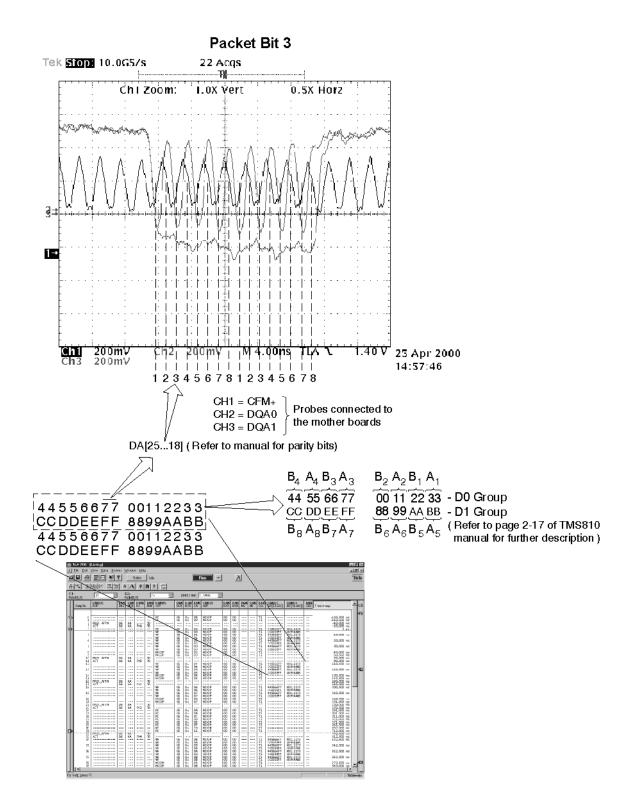

| Figure 2–8: Expanded View of Packet Bit 3                                    | 2–26 |

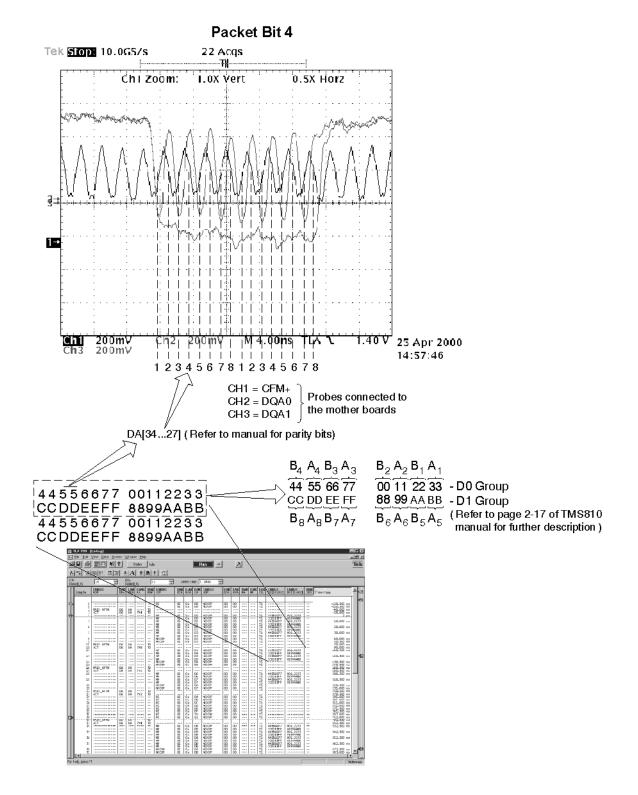

| Figure 2–9: Expanded View of Packet Bit 4                                    | 2–27 |

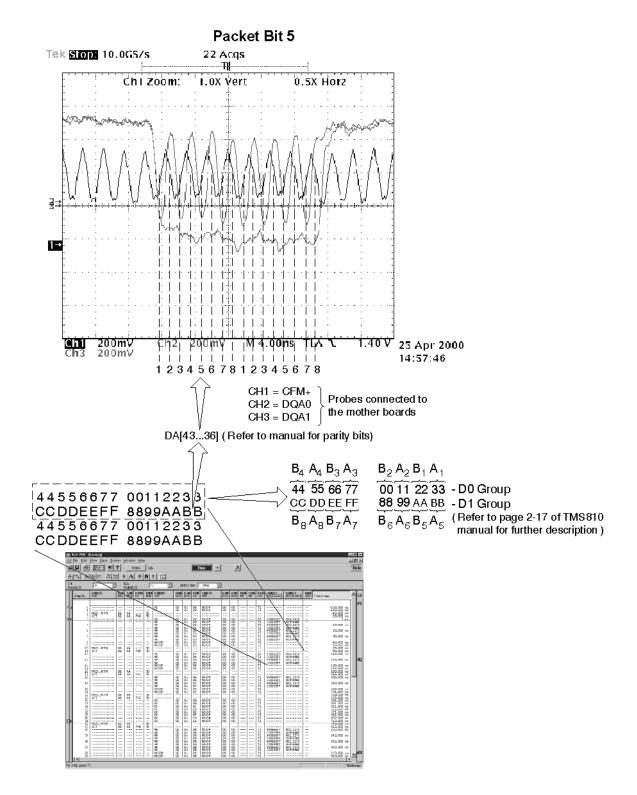

| Figure 2–10: Expanded View of Packet Bit 5                                   | 2–28 |

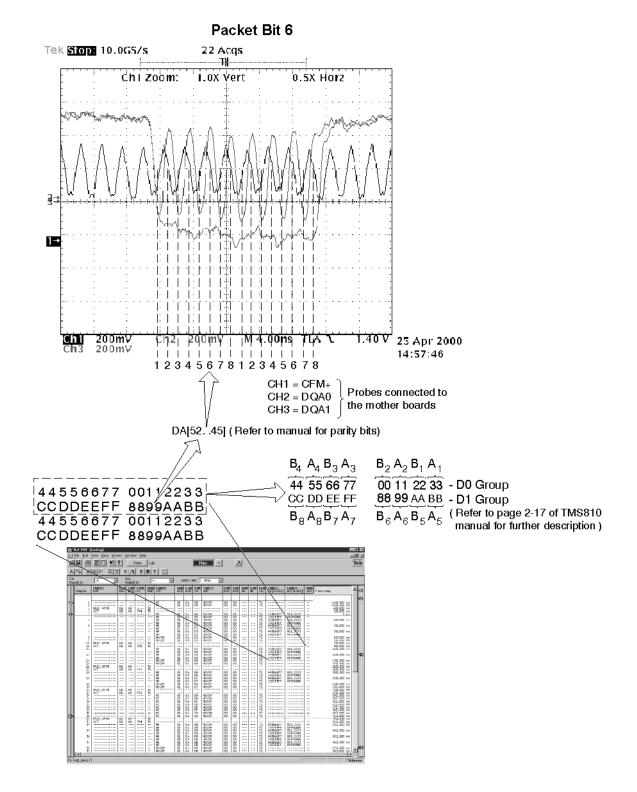

| Figure 2–11: Expanded View of Packet Bit 6                                   | 2–29 |

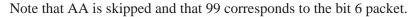

| Figure 2–12: Expanded View of Packet Bit 7                                   | 2–30 |

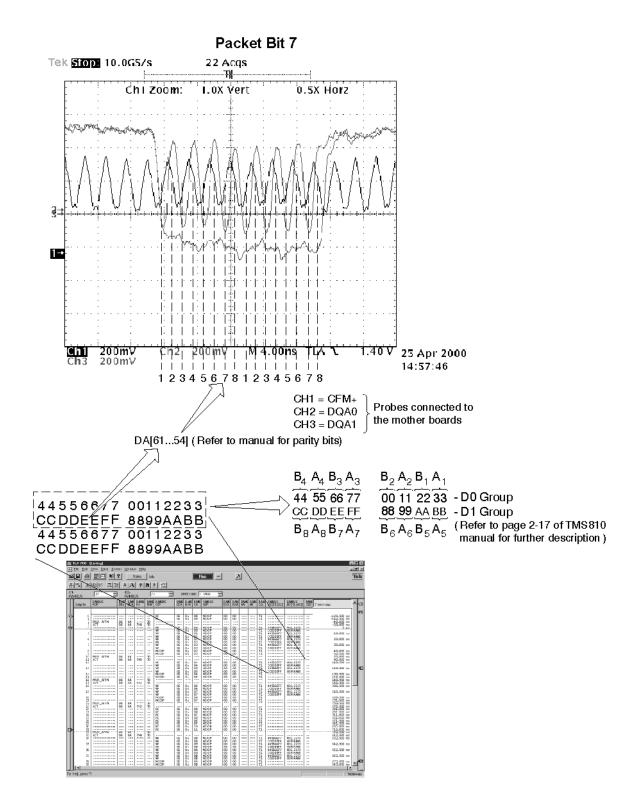

| Figure 2–13: Expanded View of Packet Bit 8                                   | 2–31 |

|                                                                              |      |

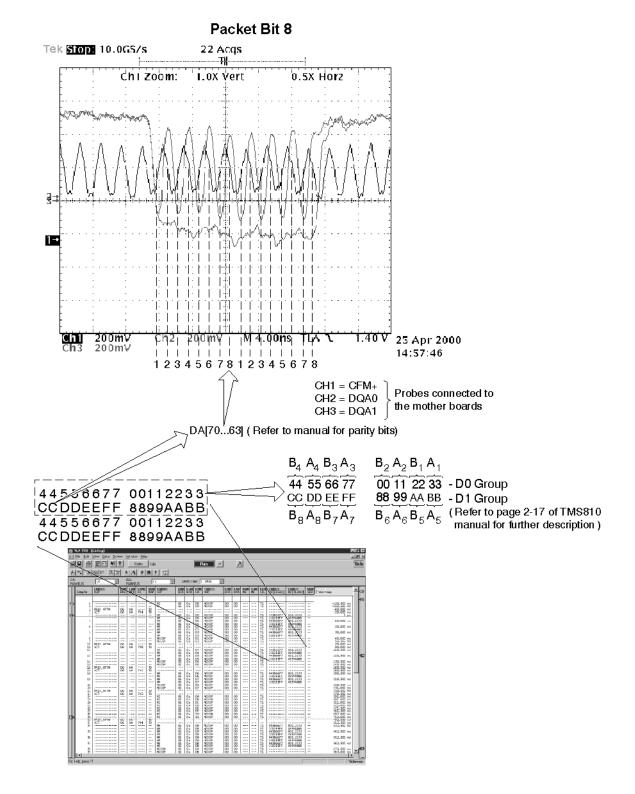

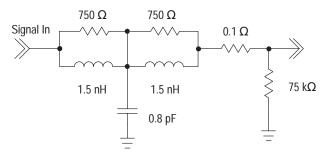

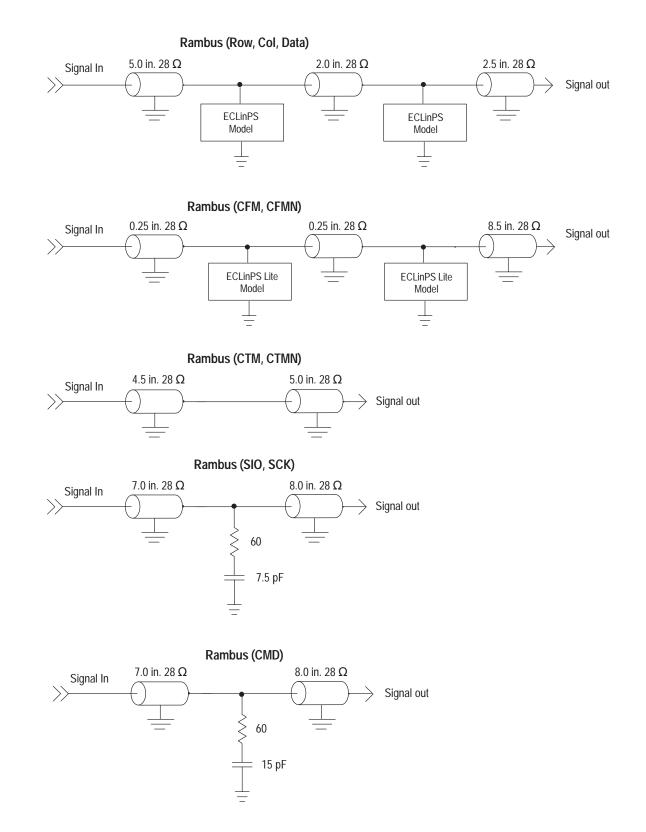

| Figure 3–1: Electrical load model                                            | 3–2  |

| Figure 3–2: Electrical load model                                            | 3–3  |

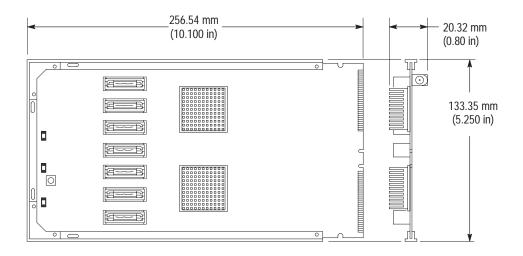

| Figure 3–3: Dimensions of the Rambus Direct probe adapter                    | 3–4  |

|                                                                              |      |

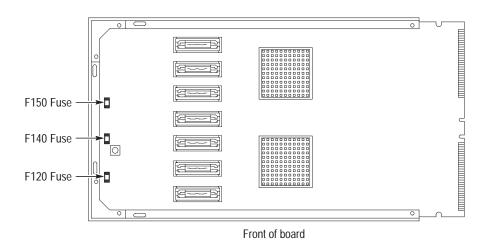

| Figure 4–1: Fuse location on the Rambus Direct probe adapter                 | 4–1  |

### List of Tables

| Table 1–1: Row Opcode channel group assignments              | 1–12 |

|--------------------------------------------------------------|------|

| Table 1–2: Device Row Address channel group assignments      | 1–13 |

| Table 1–3: Bank Row Address channel group assignments        | 1-13 |

| Table 1–4: Row Address channel group assignments             | 1–14 |

| Table 1–5: Row Packet channel group assignments              | 1–14 |

| Table 1–6: Column Opcode channel group assignments           | 1–15 |

| Table 1–7: Device Column Address channel group assignments   | 1–15 |

| Table 1–8: Bank Column Address channel group assignments     | 1–15 |

| Table 1–9: Column Address channel group assignments          | 1–16 |

| Table 1–10: XOP Opcode channel group assignments             | 1–16 |

| Table 1–11: Device XOP Address channel group assignments     | 1–17 |

| Table 1–12: Bank XOP Address channel group assignments       | 1–17 |

| Table 1–13: Mask A channel group assignments                 | 1–18 |

| Table 1–14: Mask B channel group assignments                 | 1–18 |

| Table 1–15: Column Packet channel group assignments          | 1–19 |

| Table 1–16: D0[63:32] channel group assignments              | 1–19 |

| Table 1–17: D0[31:00] channel group assignments              | 1–20 |

| Table 1–18: D1[63:32] channel group assignments              | 1–21 |

| Table 1–19: D1[31:00] channel group assignments              | 1–23 |

| Table 1–20: DA[63:32] channel group assignments              | 1–24 |

| Table 1–21: DA[31:00] channel group assignments              | 1–25 |

| Table 1–22: DB[63:32] channel group assignments              | 1–26 |

| Table 1–23: DB[31:00] channel group assignments              | 1–28 |

| Table 1–24: P0 channel group assignments                     | 1–29 |

| Table 1–25: P1 channel group assignments                     | 1–29 |

| Table 1–26: PA channel group assignments                     | 1–30 |

| Table 1–27: PB channel group assignments                     | 1–30 |

| Table 1–28: SIO channel group assignments                    | 1–31 |

| Table 1–29: Misc channel group assignments                   | 1–31 |

| Table 1–30: Signals not required for disassembly.            | 1–31 |

| Table 1–31: Row Packets                                      | 1–33 |

| Table 1–32: Column Packets                                   | 1–34 |

| Table 1–33: Write Data A Packets                             | 1–35 |

| Table 1–34: Write Data B Packets                             | 1–38 |

|                                                              |      |

| Table 2–1: Symbol table information                          | 2–8  |

| Table 2–2: Device Row Address group symbol table definitions | 2–8  |

### List of Tables (Cont.)

| Table 2–3: Row Opcode group symbol table definitions         | 2–10 |

|--------------------------------------------------------------|------|

| Table 2–4: Column Opcode group symbol table definitions      | 2–11 |

| Table 2–5: XOP Opcode group symbol table definitions         | 2–13 |

| Table 2–6: Serial I/O group symbol table definitions         | 2–14 |

| Table 2–7: Row Packet group symbol table definitions         | 2–14 |

| Table 2–8: Column Packet group symbol table definitions      | 2–14 |

| Table 2–9: Rambus Clock Cycle Time Differences               | 2–15 |

| Table 2–10: Description of special characters in the display | 2–18 |

|                                                              |      |

| Table 3–1: Electrical specifications                         | 3–1  |

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

To Avoid Fire or<br/>Personal InjuryUse Proper Power Cord. Use only the power cord specified for this product and<br/>certified for the country of use.

**Ground the Product**. This product is indirectly grounded through the grounding conductor of the mainframe power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings**. To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Use Proper AC Adapter. Use only the AC adapter specified for this product.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

#### Symbols and Terms

WARNING. Warning statements identify conditions or practices that could result in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in damage to this product or other property.

Terms on the Product. These terms may appear on the product:

Terms in this Manual. These terms may appear in this manual:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

Double

WARNING High Voltage

# Service Safety Summary

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone**. Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power**. To avoid electric shock, switch off the instrument power, then disconnect the power cord from the mains power.

**Use Care When Servicing With Power On**. Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

### Preface

This instruction manual contains specific information about the TMS 810 Rambus Direct Support package and is part of a set of information on how to operate this product on compatible Tektronix logic analyzers.

If you are familiar with operating Microprocessor or bus support packages on the logic analyzer for which the TMS 810 Rambus Direct Support was purchased, you will only need this instruction manual to set up and run the support.

#### **Manual Conventions**

This manual uses the following conventions:

- The term "disassembler" refers to the software that decodes bus cycles into instruction mnemonics and cycle types.

- The phrase "information on basic operations" refers to online help, an installation manual, or a user manual covering the basic operations of Rambus Direct support.

- The term "logic analyzer" refers to the Tektronix logic analyzer for which this product was purchased.

- The term "HI module" refers to the module in the higher-numbered slot and the term "LO module" refers to the module in the lower-numbered slot.

The portable logic analyzer has the lower numbered slots on the top and the benchtop logic analyzer has the lower numbered slots on the left.

### **Contacting Tektronix**

| Phone             | 1-800-833-9200*                                                                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Address           | Tektronix, Inc.<br>Department or name (if known)<br>14200 SW Karl Braun Drive<br>P.O. Box 500<br>Beaverton, OR 97077<br>USA |

| Web site          | www.tektronix.com                                                                                                           |

| Sales support     | 1-800-833-9200, select option 1*                                                                                            |

| Service support   | 1-800-833-9200, select option 2*                                                                                            |

| Technical support | Email: techsupport@tektronix.com                                                                                            |

|                   | 1-800-833-9200, select option 3*<br>1-503-627-2400                                                                          |

|                   | 6:00 a.m. – 5:00 p.m. Pacific time                                                                                          |

\* This phone number is toll free in North America. After office hours, please leave a voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

# **Getting Started**

### **Getting Started**

This chapter contains the following information on the TMS 810 Rambus Direct support package: configuring the probe adapter, connecting the logic analyzer to the system under test, and applying power to the probe adapter.

### **Support Package Description**

The TMS 810 Rambus Direct support package displays disassembled data from systems based on the Rambus.

To use this support efficiently, refer to information on basic operations in your online help and the following documents:

- Direct Rambus RIMM Module Specification, Rambus, Inc., 1998

- Direct Rambus Technical Description, Rambus, Inc., 1998

Information on basic operations also contains a general description of support.

### Logic Analyzer Software Compatibility

The label on the TMS 810 Rambus support floppy disk states which version of logic analyzer software the support is compatible with.

### Logic Analyzer Configuration

To use the TMS 810 Rambus support package you need a Tektronix logic analyzer equipped with the following modules: a combination of one 136-channel and one 102-channel, or two 136-channel modules. The 136-channel module must be in the lower numbered slot. The modules must be in adjacent slots and merged. The suggested module speed is a minimum of 100 MHz.

#### **Requirements and Restrictions**

Review electrical specifications in the *Specifications* chapter on pages 3–1 as they pertain to your system under test, as well as the following descriptions of other TMS 810 Rambus Direct support package requirements and restrictions.

**System Clock Rate**. The TMS 810 Rambus Direct support package can acquire data from the Rambus module operating at speeds of up to 400 MHz. The TMS 810 Rambus Direct support package has been tested to this clock rate. This specification is valid at the time this manual was printed. Contact your Tektronix sales representative for current information on the fastest devices supported.

**Non-Intrusive Acquisition**. The TMS 810 Rambus Direct probe adapter will not intercept, modify, or present signals back to the system under test.

### **Functionality Not Supported**

Read Data. Read Data is not supported.

Range Recognizers. Range Recognizers are not supported.

Serial Presence Detect. Serial Presence Detect is not supported.

**Control Register Transactions.** Control register transactions, which use the SIO bus, are not supported, but Power State Transitions for NAP/PDN Exit, which also use the SIO bus, are supported. However, the TMS 810 Rambus Direct support package will only indicate power state transitions for NAP/PDN Exit, as indicated by the SIO bus, and will not track the present power state of the RDRAM devices.

### Connecting the Logic Analyzer to the SUT

Your system under test (SUT); must have a minimum amount of clearance surrounding the Rambus Direct RIMM socket to accommodate the probe adapter.

To connect the logic analyzer to a system under test using the probe adapter, follow these steps:

**1.** Turn off power to your system under test. It is not necessary to turn off power to the logic analyzer.

**CAUTION.** To prevent static damage, handle these components only in a staticfree environment. Static discharge can damage the Rambus Direct probe adapter, the probes, and the logic analyzer module.

Always wear a grounding wrist strap, heel strap, or similar device while handling the Rambus Direct probe adapter.

- 2. To discharge your stored static electricity, touch the ground connector located on the back of the logic analyzer. Then, before you remove the probe adapter from the protective bag it is shipped in, touch the bag to discharge stored static electricity from the probe adapter.

- 3. Place the system under test on a horizontal static-free surface.

- 4. Remove the Rambus Direct RIMM module from your system under test, using the latch release levers on the RIMM socket. Store the Rambus Direct RIMM module in a static free protective bag.

- 5. Remove the probe adapter from the protective packaging.

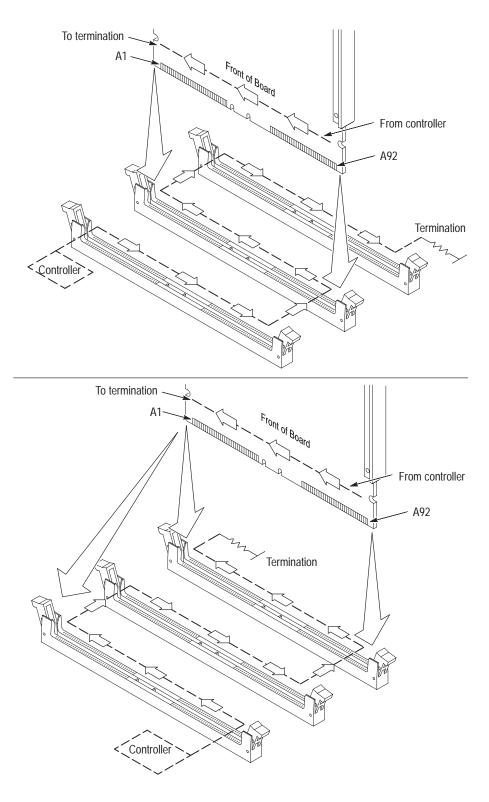

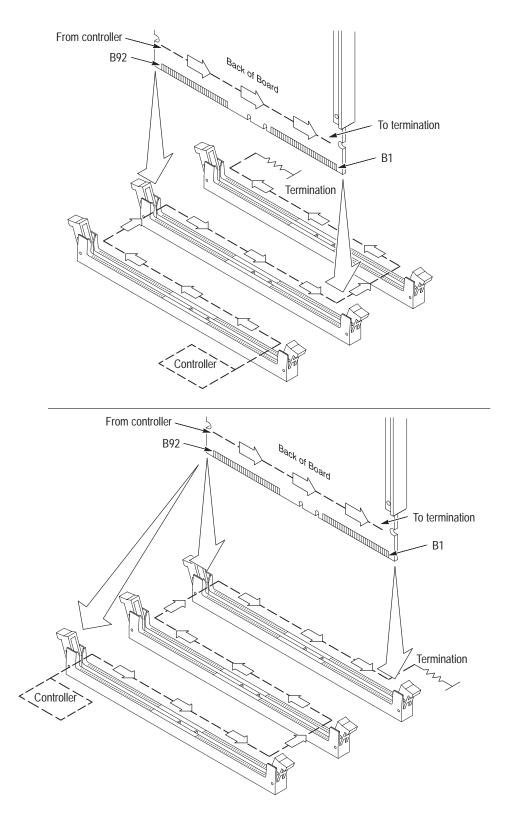

**NOTE**. To prevent incorrect acquisition, both the probe adapter and the Rambus Direct RIMM connectors must be connected with their signal-flow moving in the same direction, from controller to termination. Figures 1–1 and 1–2 show the four signal-flow variations.

6. Using Figures 1–1 or 1–2, choose which variation is like your system under test. Notice that in two of the configurations the probe adapter can be installed in the first or last RIMM socket, whereas in the other two configurations the probe adapter can only be installed in the middle RIMM socket.

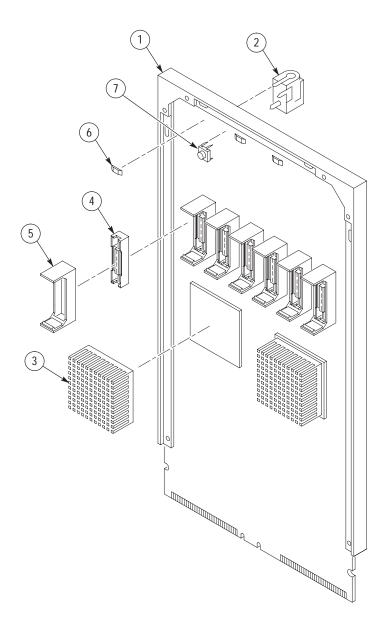

Figure 1–1: Identify slot(s) for probe adapter insertion (front of board)

Figure 1–2: Identify slot(s) for probe adapter insertion (back of board)

**CAUTION.** To prevent damage to the Rambus Direct RIMM connector on the system under test do not twist or bend the probe adapter while inserting it into the system under test.

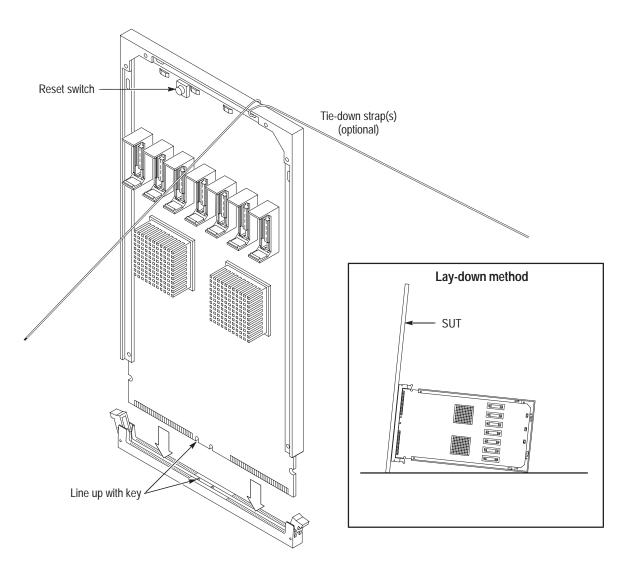

7. Insert the probe adapter into the *Rambus Direct RIMM* connector on the system under test as shown in Figure 1–3.

Figure 1–3: Connecting the probe adapter to the system under test.

**8.** Optional: Attach a tie-down strap(s) through the slot(s) on the probe adapter, and then to the SUT or the benchtop (see Figure 1–3). This step minimizes movement in the Rambus Direct RIMM connector after insertion of the probe adapter.

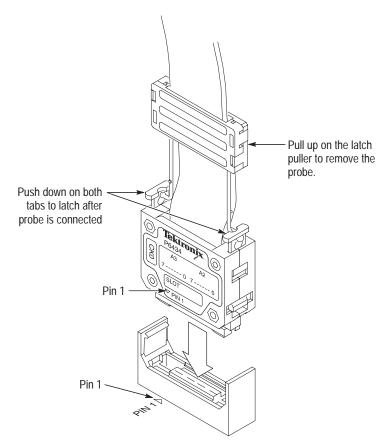

**CAUTION.** To prevent damage to the probe and probe adapter, always position the probe perpendicular to the mating connector and gently connect the probe. Incorrect handling of the P6434 probe while connecting it to the probe adapter can result in damage to the probe or to the mating connector on the probe adapter.

**9.** Use the P6434 probes to connect to the Mictor connectors on the Rambus probe adapter. Match the A, C, D and E, probes from the LO module with the corresponding LO\_A, LO\_C, LO\_D and LO\_E probe connectors on the probe adapter. Match the A, C, and D probes from the HI module with corresponding HI\_A, HI\_C, and HI\_D probe connections on the probe adapter. Align the pin 1 indicator on the probe label with the pin 1 of the connector on the probe adapter.

The module in the higher-numbered slot is referred to as the slave module, and the module in the lower-numbered slot is referred to as the master module.

**10.** Position the probe tip perpendicular to the mating connector and gently connect the probe as shown in Figure 1–4.

Figure 1–4: Connecting a probe to the connector on the probe adapter

- **11.** When connected, push down on the latch releases on the probe to set the latch.

- 12. Repeat steps 10 and 11 for the remaining probes.

- **13.** Connect the module ends of the P6434 probes to the corresponding connectors (match label colors) on the logic analyzer. The probe module ends are polarized.

#### Applying and Removing Power

The power supplies for the TMS 810 Rambus Direct probe adapter are included with this TMS 810 Rambus Direct support package. The power supplies provide +5 volts to the probe adapter.

**CAUTION.** To prevent damage to the probe adapter, remove power from the probe adapter whenever you power off the system under test.

To apply power to the Rambus probe adapter, follow these steps:

**CAUTION.** To prevent permanent damage to the probe adapter, use the +5 V power supplies provided by Tektronix. Do not mistake similar power supplies for the +5 V power supplies.

1. Connect the +5 V power supplies to the jacks on the probe adapter. Figure 1–5 shows the location of the jacks on the probe adapter board.

**CAUTION.** To prevent damage to the system under test, apply power to the probe adapter before applying power to your system under test.

- **2.** Plug the power supplies for the probe adapter into an electrical outlet. When power is present on the probe adapter, an LED lights near each power jack.

- **3.** Power on the system under test.

Figure 1–5: Location of the power jacks

To remove power from the system under test and the probe adapter, follow these steps:

**CAUTION.** To prevent damage to the system under test, remove power from your system under test before removing power from the probe adapter.

- 1. Power off the system under test.

- 2. Unplug the power supplies from the probe adapter from the electrical outlet.

**Reset Switch** You can issue a reset by pressing the button on top of the reset switch (see Figure 1–6 for location).

**NOTE**. If either of the following conditions occur you must reset the probe adapter or you will acquire incorrect data: any time the Rambus clock has been stopped and restarted or power to the SUT is turned off and on again. Pressing the Reset button has no effect on the SUT.

Figure 1–6: Location of the Reset switch

### Removing the Probe Adapter from the SUT

To remove the Rambus Direct probe adapter from the system under test, follow these steps:

**CAUTION.** To prevent static damage, handle the components only in a static-free environment. Static discharge can damage the Rambus Direct RIMM module, the probe adapter, the probes, and the logic analyzer module.

Always wear a grounding wrist strap, heel strap or similar device while handling the Rambus Direct module and probe adapter.

- **1.** Power off your system under test and the probe adapter. It is not necessary to power off the logic analyzer.

- 2. Disconnect the +5 V power supplies from the jacks on the probe adapter.

- **3.** Disconnect the probes from the probe adapter assembly. Use the latch puller to release the probes.

- 4. Release the tie-downs from your system under test or bench top.

**CAUTION.** To prevent damage to the Rambus Direct RIMM connectors carefully perform step 5.

- **5.** Disconnect the probe adapter from your system under test using the latch release levers on the Rambus Direct RIMM socket.

- 6. Place the probe adapter back into the protective bag it was shipped in.

- 7. Reinstall the Rambus Direct RIMM module into your system under test.

#### **Channel Assignments**

Channel assignments listed in Tables 1–2 through Table 1–29 use the following conventions:

- All signals are required by the support unless indicated otherwise.

- Channels are listed starting with the most significant bit (MSB) descending to the least significant bit (LSB).

- Channel group assignments are for all modules unless otherwise noted.

- The module in the higher-numbered slot is referred to as the HI module and the module in the lower-numbered slot is referred to as the LO module.

The portable logic analyzer has the lower numbered slot on the top and the benchtop logic analyzer has the lower numbered slot on the left.

The following are Rambus channel groups:

| ROP | MA        | P1   |

|-----|-----------|------|

| DRA | MB        | PA   |

| BRA | COL       | PB   |

| RA  | D0[63:32] | SIO  |

| ROW | D0[31:00] | Misc |

| COP | D1[63:32] |      |

| DCA | D1[31:00] |      |

| BCA | DA[63:32] |      |

| CA  | DA[31:00] |      |

| XOP | DB[63:32] |      |

| DXA | DB[31:00] |      |

| BXA | P0        |      |

Table 1–1 lists the Rambus signals for each channel of the Row Opcode group. By default the ROP channel group assignments are displayed as symbols. The symbol table file name is Rambus\_ROP.

Table 1–1: Row Opcode channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 12           | ROW-VALID             |

| 11           | AV                    |

| 10           | ROP10                 |

| 9            | ROP9                  |

| 8            | ROP8                  |

| 7            | ROP7                  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 6            | ROP6                  |

| 5            | ROP5                  |

| 4            | ROP4                  |

| 3            | ROP3                  |

| 2            | ROP2                  |

| 1            | ROP1                  |

| 0            | ROP0                  |

Table 1–1: Row Opcode channel group assignments (Cont.)

Table 1–2 lists the Rambus signals for each channel of the Device Row Address group. By default the DRA channel group assignments are displayed as symbols. The symbol table file name is Rambus\_DRA.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 6            | ROW-VALID             |

| 5            | DR4T                  |

| 4            | DR4F                  |

| 3            | DR3                   |

| 2            | DR2                   |

| 1            | DR1                   |

| 0            | DR0                   |

Table 1–3 lists the Rambus signals for each channel the Bank Row Address group. By default the BRA channel group assignments are displayed as hexadecimal.

| Table 1–3: Bank Row Address channel group |  |

|-------------------------------------------|--|

| assignments                               |  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 5            | BR5                   |

| 4            | BR4                   |

| 3            | BR3                   |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 2            | BR2                   |

| 1            | BR1                   |

| 0            | BR0                   |

Table 1–3: Bank Row Address channel group assignments (Cont.)

Table 1–4 lists the Rambus signals for each channel the Row Address group. By default the RA channel group assignments are displayed as hexadecimal.

Bit Rambus order signal name 10 R10 9 R9 8 R8 7 R7 6 R6 5 R5 4 R4 3 R3 2 R2 1 R1 0 R0

Table 1–4: Row Address channel group assignments

Table 1–5 lists the Rambus signals for each channel of the Row Packet group. By default the ROW channel group assignments are displayed as symbols. The symbol table file name is Rambus\_ROW.

Table 1–5: Row Packet channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 2            | ROW-VALID             |

| 1            | ROW-TMG1              |

| 0            | ROW-TMG0              |

Table 1–6 lists the Rambus signals for each channel of the Column Opcode group. By default the COP channel group assignments are displayed as symbols. The symbol table file name is Rambus\_COP.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 5            | COL-VALID             |

| 4            | S                     |

| 3            | COP3                  |

| 2            | COP2                  |

| 1            | COP1                  |

| 0            | COP0                  |

Table 1–6: Column Opcode channel group assignments

Table 1–7 lists the Rambus signals for each channel of the Device Column Address group. By default the DCA channel group assignments are displayed as hexadecimal.

| Table 1–7: Device Column Address channel group |  |

|------------------------------------------------|--|

| assignments                                    |  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 4            | DC4                   |

| 3            | DC3                   |

| 2            | DC2                   |

| 1            | DC1                   |

| 0            | DC0                   |

Table 1–8 lists the Rambus signals for each channel of the Bank Column Address group. By default the BCA channel group assignments are displayed as hexadecimal.

Table 1–8: Bank Column Address channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 5            | BC5                   |

| 4            | BC4                   |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 3            | BC3                   |

| 2            | BC2                   |

| 1            | BC1                   |

Table 1–8: Bank Column Address channel group assignments (Cont.)

Table 1–9 lists the Rambus signals for each channel of the Column Address group. By default the CA channel group assignments are displayed as hexadecimal.

### Table 1–9: Column Address channel group assignments

BC0

0

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 6            | C6                    |

| 5            | C5                    |

| 4            | C4                    |

| 3            | C3                    |

| 2            | C2                    |

| 1            | C1                    |

| 0            | CO                    |

Table 1–10 lists the Rambus signals for each channel of the XOP Opcode group. By default the XOP channel group assignments are displayed as symbols. The symbol table file name is Rambus\_XOP.

Table 1–10: XOP Opcode channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | COL-VALID             |

| 6            | S                     |

| 5            | M                     |

| 4            | XOP4                  |

| 3            | XOP3                  |

| 2            | XOP2                  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 1            | XOP1                  |

| 0            | XOP0                  |

Table 1–10: XOP Opcode channel group assignments (Cont.)

Table 1–11 lists the Rambus signals for each channel of the Device XOP Address group. By default the DXA channel group assignments are displayed as hexadecimal.

### Table 1–11: Device XOP Address channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 4            | DX4                   |

| 3            | DX3                   |

| 2            | DX2                   |

| 1            | DX1                   |

| 0            | DX0                   |

Table 1–12 lists the Rambus signals for each channel of the Bank XOP Address group. By default the BXA channel group assignments are displayed as hexadecimal.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 5            | BX5                   |

| 4            | BX4                   |

| 3            | BX3                   |

| 2            | BX2                   |

| 1            | BX1                   |

| 0            | BX0                   |

### Table 1–12: Bank XOP Address channel group assignments

Table 1–13 lists the Rambus signals for each channel of Mask A group. By default the MA channel group assignments are displayed in hexadecimal.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | MA7                   |

| 6            | MA6                   |

| 5            | MA5                   |

| 4            | MA4                   |

| 3            | MA3                   |

| 2            | MA2                   |

| 1            | MA1                   |

| 0            | MAO                   |

Table 1–13: Mask A channel group assignments

Table 1–14 lists the Rambus signals for each channel of Mask B group. By default the MB channel group assignment is displayed in hexadecimal.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | MB7                   |

| 6            | MB6                   |

| 5            | MB5                   |

| 4            | MB4                   |

| 3            | MB3                   |

| 2            | MB2                   |

| 1            | MB1                   |

| 0            | MB0                   |

Table 1–14: Mask B channel group assignments

Table 1–15 lists the Rambus signals for each channel of the Column Packet group. By default the COL channel group assignments are displayed as symbols. The symbol table file name is Rambus\_COL.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 2            | COL-VALID             |

| 1            | COL-TMG1              |

| 0            | COL-TMG0              |

Table 1–15:

Column Packet channel group assignments

Table 1–16 lists the Rambus signals for each channel of the D0[63:32] group. By default the D0[63:32] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Front Side Bus byte order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB34                  |

| 30           | DB33                  |

| 29           | DB32                  |

| 28           | DB31                  |

| 27           | DB30                  |

| 26           | DB29                  |

| 25           | DB28                  |

| 24           | DB27                  |

| 23           | DA34                  |

| 22           | DA33                  |

| 21           | DA32                  |

| 20           | DA31                  |

| 19           | DA30                  |

| 18           | DA29                  |

| 17           | DA28                  |

| 16           | DA27                  |

| 15           | DB25                  |

| 14           | DB24                  |

| Table 1–16: D0[63:32] | channel grou | o assignments |

|-----------------------|--------------|---------------|

|                       |              |               |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 13           | DB23                  |

| 12           | DB22                  |

| 11           | DB21                  |

| 10           | DB20                  |

| 9            | DB19                  |

| 8            | DB18                  |

| 7            | DA25                  |

| 6            | DA24                  |

| 5            | DA23                  |

| 4            | DA22                  |

| 3            | DA21                  |

| 2            | DA20                  |

| 1            | DA19                  |

| 0            | DA18                  |

Table 1–16: D0[63:32] channel group assignments (Cont.)

Table 1–17 lists the Rambus signals for each channel of the D0[31:00] group. By default the D0[31:00] channel group assignments are displayed in hexadecimal. This channel group assignment matches the Front Side Bus byte order.

Table 1–17: D0[31:00] channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB16                  |

| 30           | DB15                  |

| 29           | DB14                  |

| 28           | DB13                  |

| 27           | DB12                  |

| 26           | DB11                  |

| 25           | DB10                  |

| 24           | DB9                   |

| 23           | DA16                  |

| 22           | DA15                  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 21           | DA14                  |

| 20           | DA13                  |

| 19           | DA12                  |

| 18           | DA11                  |

| 17           | DA10                  |

| 16           | DA9                   |

| 15           | DB7                   |

| 14           | DB6                   |

| 13           | DB6                   |

| 12           | DB4                   |

| 11           | DB3                   |

| 10           | DB2                   |

| 9            | DB1                   |

| 8            | DB0                   |

| 7            | DA7                   |

| 6            | DA6                   |

| 5            | DA5                   |

| 4            | DA4                   |

| 3            | DA3                   |

| 2            | DA2                   |

| 1            | DA1                   |

| 0            | DA0                   |

|              |                       |

Table 1–17: D0[31:00] channel group assignments (Cont.)

Table 1–18 lists the Rambus signals for each channel of the D1[63:32] group. By default the D1[63:32] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Front Side Bus byte order.

| Table 1–18: D1[63:32] | channel group | assignments |

|-----------------------|---------------|-------------|

|-----------------------|---------------|-------------|

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB70                  |

| 30           | DB69                  |

| 29         DB68           28         DB67           27         DB66           26         DB65           25         DB64           24         DB63           23         DA70 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 27         DB66           26         DB65           25         DB64           24         DB63                                                                               |  |

| 26         DB65           25         DB64           24         DB63                                                                                                         |  |

| 25         DB64           24         DB63                                                                                                                                   |  |

| 24 DB63                                                                                                                                                                     |  |

|                                                                                                                                                                             |  |

| 23 DA70                                                                                                                                                                     |  |

|                                                                                                                                                                             |  |

| 22 DA69                                                                                                                                                                     |  |

| 21 DA68                                                                                                                                                                     |  |

| 20 DA67                                                                                                                                                                     |  |

| 19 DA66                                                                                                                                                                     |  |

| 18 DA65                                                                                                                                                                     |  |

| 17 DA64                                                                                                                                                                     |  |

| 16 DA63                                                                                                                                                                     |  |

| 15 DB61                                                                                                                                                                     |  |

| 14 DB60                                                                                                                                                                     |  |

| 13 DB59                                                                                                                                                                     |  |

| 12 DB58                                                                                                                                                                     |  |

| 11 DB57                                                                                                                                                                     |  |

| 10 DB56                                                                                                                                                                     |  |

| 9 DB55                                                                                                                                                                      |  |

| 8 DB54                                                                                                                                                                      |  |

| 7 DA61                                                                                                                                                                      |  |

| 6 DA60                                                                                                                                                                      |  |

| 5 DA59                                                                                                                                                                      |  |

| 4 DA58                                                                                                                                                                      |  |

| 3 DA57                                                                                                                                                                      |  |

| 2 DA56                                                                                                                                                                      |  |

| 1 DA55                                                                                                                                                                      |  |

| 0 DA54                                                                                                                                                                      |  |

Table 1-18: D1[63:32] channel group assignments (Cont.)

Table 1–19 lists the Rambus signals for each channel of the D1[31:00] group. By default the D1[31:00] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Front Side Bus byte order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB52                  |

| 30           | DB51                  |

| 29           | DB50                  |

| 28           | DB49                  |

| 27           | DB48                  |

| 26           | DB47                  |

| 25           | DB46                  |

| 24           | DB45                  |

| 23           | DA52                  |

| 22           | DA51                  |

| 21           | DA50                  |

| 20           | DA49                  |

| 19           | DA48                  |

| 18           | DA47                  |

| 17           | DA46                  |

| 16           | DA45                  |

| 15           | DB43                  |

| 14           | DB42                  |

| 13           | DB41                  |

| 12           | DB40                  |

| 11           | DB39                  |

| 10           | DB38                  |

| 9            | DB37                  |

| 8            | DB36                  |

| 7            | DA43                  |

| 6            | DA42                  |

| 5            | DA41                  |

| 4            | DA40                  |

| 3            | DA39                  |

| 2            | DA38                  |

Table 1–19: D1[31:00] channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 1            | DA37                  |

| 0            | DA36                  |

Table 1–19: D1[31:00] channel group assignments (Cont.)

Table 1–20 lists the Rambus signals for each channel of the DA[63:32] group. By default the DA[63:32] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Rambus transmission byte order.

|              | Dambar                |

|--------------|-----------------------|

| Bit<br>order | Rambus<br>signal name |

| 31           | DA70                  |

| 30           | DA69                  |

| 29           | DA68                  |

| 28           | DA67                  |

| 27           | DA66                  |

| 26           | DA65                  |

| 25           | DA64                  |

| 24           | DA63                  |

| 23           | DA61                  |

| 22           | DA60                  |

| 21           | DA59                  |

| 20           | DA58                  |

| 19           | DA57                  |

| 18           | DA56                  |

| 17           | DA55                  |

| 16           | DA54                  |

| 15           | DA52                  |

| 14           | DA51                  |

| 13           | DA50                  |

| 12           | DA49                  |

| 11           | DA48                  |

| 10           | DA47                  |

| 9            | DA46                  |

Table 1–20: DA[63:32] channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 8            | DA45                  |

| 7            | DA43                  |

| 6            | DA42                  |

| 5            | DA41                  |

| 4            | DA40                  |

| 3            | DA39                  |

| 2            | DA38                  |

| 1            | DA37                  |

| 0            | DA36                  |

Table 1–20: DA[63:32] channel group assignments (Cont.)

Table 1–21 lists the Rambus signals for each channel of the DA[31:00] group. By default the DA[31:00] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Rambus Transmission byte order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DA34                  |

| 30           | DA33                  |

| 29           | DA32                  |

| 28           | DA31                  |

| 27           | DA30                  |

| 26           | DA29                  |

| 25           | DA28                  |

| 24           | DA27                  |

| 23           | DA25                  |

| 22           | DA24                  |

| 21           | DA23                  |

| 20           | DA22                  |

| 19           | DA21                  |

| 18           | DA20                  |

| 17           | DA19                  |

| 16           | DA18                  |

Table 1–21: DA[31:00] channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 15           | DA16                  |

| 14           | DA15                  |

| 13           | DA14                  |

| 12           | DA13                  |

| 11           | DA12                  |

| 10           | DA11                  |

| 9            | DA10                  |

| 8            | DA9                   |

| 7            | DA7                   |

| 6            | DA6                   |

| 5            | DA5                   |

| 4            | DA4                   |

| 3            | DA3                   |

| 2            | DA2                   |

| 1            | DA1                   |

| 0            | DA0                   |

Table 1–21: DA[31:00] channel group assignments (Cont.)

Table 1–22 lists the Rambus signals for each channel of the DB[63:32] group. By default the DB[63:32] channel group assignments are displayed in hexadecimal. This channel group assignment matches the Rambus Transmission order.

| Table 1–22: DB[63:32 | channel gro | up assignments |

|----------------------|-------------|----------------|

|----------------------|-------------|----------------|

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB70                  |

| 30           | DB69                  |

| 29           | DB68                  |

| 28           | DB67                  |

| 27           | DB66                  |

| 26           | DB65                  |

| 25           | DB64                  |

| 24           | DB63                  |

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 23           | DB61                  |

| 22           | DB60                  |

| 21           | DB59                  |

| 20           | DB58                  |

| 19           | DB57                  |

| 18           | DB56                  |

| 17           | DB55                  |

| 16           | DB54                  |

| 15           | DB52                  |

| 14           | DB51                  |

| 13           | DB50                  |

| 12           | DB49                  |

| 11           | DB48                  |

| 10           | DB47                  |

| 9            | DB46                  |

| 8            | DB45                  |

| 7            | DA43                  |

| 6            | DA42                  |

| 5            | DA41                  |

| 4            | DA40                  |

| 3            | DA39                  |

| 2            | DA38                  |

| 1            | DA37                  |

| 0            | DA36                  |

Table 1–22: DB[63:32] channel group assignments (Cont.)

Table 1–23 lists the Rambus signals for each channel of the DB[31:00] group. By default the DB[31:00] channel group assignment is displayed in hexadecimal. This channel group assignment matches the Rambus Transmission order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 31           | DB34                  |

| 30           | DB33                  |

| 29           | DB32                  |

| 28           | DB31                  |

| 27           | DB30                  |

| 26           | DB29                  |

| 25           | DB28                  |

| 24           | DB27                  |

| 23           | DB25                  |

| 22           | DB24                  |

| 21           | DB23                  |

| 20           | DB22                  |

| 19           | DB21                  |

| 18           | DB20                  |

| 17           | DB19                  |

| 16           | DB18                  |

| 15           | DB16                  |

| 14           | DB15                  |

| 13           | DB14                  |

| 12           | DB13                  |

| 11           | DB12                  |

| 10           | DB11                  |

| 9            | DB10                  |

| 8            | DB9                   |

| 7            | DB7                   |

| 6            | DB6                   |

| 5            | DB5                   |

| 4            | DB4                   |

| 3            | DB3                   |

| 2            | DB2                   |

Table 1–23: DB[31:00] channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 1            | DB1                   |

| 0            | DB0                   |

Table 1–23: DB[31:00] channel group assignments (Cont.)

Table 1–24 lists the Rambus signals for each channel of the P0 group. By default the P0 channel group assignment is not displayed. This channel group assignment matches the Front Side Bus byte order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | DB35                  |

| 6            | DA35                  |

| 5            | DB26                  |

| 4            | DA26                  |

| 3            | DB17                  |

| 2            | DA17                  |

| 1            | DB8                   |

| 0            | DA8                   |

Table 1–24: P0 channel group assignments

Table 1–25 lists the Rambus signals for each channel of the P1 group. By default the P1 channel group assignment is not displayed. This channel group assignment matches the Front Side Bus byte order.

| Table 1–25: P1 channel group assignm | ents |

|--------------------------------------|------|

|--------------------------------------|------|

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | DB71                  |

| 6            | DA71                  |

| 5            | DB62                  |

| 4            | DA62                  |

| 3            | DB53                  |

| 2            | DA53                  |

| 1            | DB44                  |

| 0            | DA44                  |

Table 1–26 lists the Rambus signals for each channel of the PA group. By default the PA channel group assignment is not displayed. This channel group assignment matches the Rambus Transmission order.

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | DA71                  |

| 6            | DA62                  |

| 5            | DA53                  |

| 4            | DA44                  |

| 3            | DA35                  |

| 2            | DA26                  |

| 1            | DA17                  |

| 0            | DA8                   |

Table 1–26: PA channel group assignments

Table 1–27 lists the Rambus signals for each channel of the PB group. By default the PB channel group assignment is not displayed. This channel group assignment matches the Rambus Transmission order.

Table 1–27: PB channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 7            | DB71                  |

| 6            | DB62                  |

| 5            | DB53                  |

| 4            | DB44                  |

| 3            | DB35                  |

| 2            | DB26                  |

| 1            | DB17                  |

| 0            | DB8                   |

Table 1–28 lists the Rambus signals for each channel of the SIO group. By default the SIO channel group assignment is displayed as symbols. The symbol table file name is Rambus\_SIO.

Table 1–28: SIO channel group assignments

| _ | Bit<br>order | Rambus<br>signal name |

|---|--------------|-----------------------|

|   | 1            | SIO-1                 |

| - | 0            | SIO-0                 |

Table 1–29 lists the Rambus signals for each channel of the Misc group. By default the Misc channel group assignment is not displayed.

Table 1–29: Misc channel group assignments

| Bit<br>order | Rambus<br>signal name |

|--------------|-----------------------|

| 1            | CLK-X1                |

| 0            | CLK-X0                |

Table 1–30 lists signals not required for disassembly.

| Table 1–30: | Signal | s not rec | uired f | or d | isassemb | )ly. |

|-------------|--------|-----------|---------|------|----------|------|

|-------------|--------|-----------|---------|------|----------|------|

| Rambus<br>signal name | AUX pin number |

|-----------------------|----------------|

| GND                   | 1              |

| SIO <sup>1</sup>      | 2              |

| SCK1                  | 3              |

| CMD <sup>1</sup>      | 4              |

1 The SIO, SCK, and CMD signals are not acquired as Control Register Transactions, but are acquired as a part of the Power State Transitions. You can use the AUX connector to probe these signals. The following is a list of signals that are not available on the probe adapter. Any of these signals can be probed from the bottom of the system under test.

| CFM <sup>1</sup>  | SCL | SA1               | $V_{DD}$                      |

|-------------------|-----|-------------------|-------------------------------|

| CFMN <sup>1</sup> | SWP | SA2               | V <sub>REF</sub> <sup>2</sup> |

| СТМ               | SDA | SV <sub>DD</sub>  |                               |

| CTMN              | SA0 | V <sub>CMOS</sub> |                               |

- <sup>1</sup> The CFM and CFMN signals are used by the probe adapter to derive the 100 MHz acquisition clock, but are not otherwise available on the probe adapter.

- 2 The V<sub>REF</sub> signal is used by the probe adapter, but is not otherwise available on the probe adapter.

The following is a list of extra acquisition channels that are not attached to the probe adapter. Extra acquisition channels are only available if the second module is a 136-channel module.

HI\_E3:7-0 HI\_E2:7-0 HI\_E1:7-0 HI\_E0:7-0 HI\_Qual:2 HI\_Qual:3

# **Packet Definitions**

Tables 1–31 through 1–34 list packet definitions.

#### Table 1–31: Row packets

|                          |                | ROWA pa        | cket definitio           | n                |                | ROWR packet definition |                          |                  |               |  |  |

|--------------------------|----------------|----------------|--------------------------|------------------|----------------|------------------------|--------------------------|------------------|---------------|--|--|

|                          |                |                | DRA<br>group             | BRA<br>group     | RA<br>group    |                        | DRA<br>group             | BRA<br>group     | ROP<br>group  |  |  |

| TLA<br>channel<br>number | Signal<br>name | ROWA<br>packet | Device<br>row<br>address | Bank row address | Row<br>address | ROWR<br>packet         | Device<br>row<br>address | Bank row address | Row<br>Opcode |  |  |

| LO_D1:5                  | ROW2-T0        | DR4T           | DR4T                     |                  |                | DR4T                   | DR4T                     |                  |               |  |  |

| LO_D1:6                  | ROW1-T0        | DR4F           | DR4F                     |                  |                | DR4F                   | DR4F                     |                  |               |  |  |

| LO_D1:7                  | ROW0-T0        | DR3            | DR3                      |                  |                | DR3                    | DR3                      |                  |               |  |  |

| HI_D1:5                  | ROW2-TI        | DR2            | DR2                      |                  |                | DR2                    | DR2                      |                  |               |  |  |

| HI_D1:6                  | ROW1-TI        | DR1            | DR1                      |                  |                | DR1                    | DR1                      |                  |               |  |  |

| HI_D1:7                  | ROW0-TI        | DR0            | DR0                      |                  |                | DR0                    | DR0                      |                  |               |  |  |

| LO_D1:2                  | ROW2-T2        | BR0            |                          | BR0              |                | BR0                    |                          | BR0              |               |  |  |

| LO_D1:3                  | ROW1-T2        | BR1            |                          | BR1              |                | BR1                    |                          | BR1              |               |  |  |

| LO_D1:4                  | ROW0-T2        | BR2            |                          | BR2              |                | BR2                    |                          | BR2              |               |  |  |

| HI_D1:2                  | ROW2-T3        | BR3            |                          | BR3              |                | BR3                    |                          | BR3              |               |  |  |

| HI_D1:3                  | ROW1-T3        | BR4            |                          | BR4              |                | BR4                    |                          | BR4              |               |  |  |

| HI_D1:4                  | ROW0-T3        | BR5            |                          | BR5              |                | BR5                    |                          | BR5              |               |  |  |

| LO_D0:7                  | ROW2-T4        | R10            |                          |                  | R10            | ROP10                  |                          |                  | ROP10         |  |  |

| LO_D1:0                  | ROW1-T4        | R9             |                          |                  | R9             | ROP9                   |                          |                  | ROP9          |  |  |

| LO_D1:1                  | ROW0-T4        | AV=1           |                          |                  | AV=1           | AV=0                   |                          |                  | AV=0          |  |  |

| HI_D0:7                  | ROW2-T5        | R8             |                          |                  | R8             | ROP8                   |                          |                  | ROP8          |  |  |

| HI_D1:0                  | ROW1-T5        | R7             |                          |                  | R7             | ROP7                   |                          |                  | ROP7          |  |  |

| HI_D1:1                  | ROW0-T5        | R6             |                          |                  | R6             | ROP6                   |                          |                  | ROP6          |  |  |

| LO_D0:4                  | ROW2-T6        | R5             |                          |                  | R5             | ROP5                   |                          |                  | ROP5          |  |  |

| LO_D0:5                  | ROW1-T6        | R4             |                          |                  | R4             | ROP4                   |                          |                  | ROP4          |  |  |

| LO_D0:6                  | ROW0-T6        | R3             |                          |                  | R3             | ROP3                   |                          |                  | ROP3          |  |  |

| HI_D0:4                  | ROW2-T7        | R2             |                          |                  | R2             | ROP2                   |                          |                  | ROP2          |  |  |

| HI_D0:5                  | ROW1-T7        | R1             |                          |                  | R1             | ROP1                   |                          |                  | ROP1          |  |  |

| HI_D0:6                  | ROW0-T7        | R0             |                          |                  | R0             | ROP0                   |                          |                  | ROP0          |  |  |

## Table 1–32: Column packets

|                          |                | COLC p         | acket def                        | inition                        |                        |                  | COLX p         | acket de                      | finition                    |               | COLM packet definition |                        |                        |

|--------------------------|----------------|----------------|----------------------------------|--------------------------------|------------------------|------------------|----------------|-------------------------------|-----------------------------|---------------|------------------------|------------------------|------------------------|

| Grou                     | ip name 🕨      |                | DCA                              | BCA                            | CA                     | СОР              |                | DXA                           | BXA                         | ХОР           |                        | MA                     | MB                     |

| TLA<br>channel<br>number | Siganl<br>name | COLC<br>packet | Device<br>column<br>ad-<br>dress | Bank<br>column<br>ad-<br>dress | Column<br>ad-<br>dress | Column<br>Opcode | COLX<br>packet | Device<br>XOP<br>ad-<br>dress | Bank<br>XOP<br>ad-<br>dress | XOP<br>Opcode | COLM<br>packet         | Mask A<br>byte<br>mask | Mask B<br>byte<br>mask |

| LO_D2:0                  | COL4-T0        | DC4            | DC4                              |                                |                        |                  |                |                               |                             |               |                        |                        |                        |

| LO_D0:0                  | COL3-T0        | DC3            | DC3                              |                                |                        |                  |                |                               |                             |               |                        |                        |                        |

| LO_D0:1                  | COL2-T0        | DC2            | DC2                              |                                |                        |                  |                |                               |                             |               |                        |                        |                        |